# Designing With Microcomputers

An Introductory Text

on

Microcomputer Fundamentals

for

Electronic Circuit and System Designers and Managers

January 1976

### **TABLE OF CONTENTS**

|                          | Preface            |                                                                            | 1              |

|--------------------------|--------------------|----------------------------------------------------------------------------|----------------|

| l.<br>1.1                | System             | DUCTION  Development Procedure                                             | 1<br>1         |

| 1.2                      | The Des<br>Typewri | ign Problem: An Intelligent ter System (ITS)                               | 2              |

| 11.                      | MICRO              | COMPUTER BASICS                                                            | 5              |

| 2.1<br>2.2<br>2.3<br>2.4 | An Aut             | ctiony Hand Calculatoron<br>omatic Calculator<br>Practical Example:        | 5<br>5<br>9    |

|                          | Mixing             | Vat                                                                        | 12             |

| 2.5<br>2.6<br>2.7<br>2.8 | Binary<br>Assemb   | Powerful Microcomputer Instructions Iler Instructions Instruction Memory — | 15<br>16<br>17 |

|                          | The Sul            | broutine                                                                   | 18             |

| 2.9<br>2.10              |                    | n Status Word                                                              | 20<br>22       |

|                          |                    | r Chapter IIs to Quiz                                                      | 25<br>26       |

| Ш.                       | OF TH              | N AND IMPLEMENTATION<br>E INTELLIGENT TYPEWRITER                           |                |

|                          |                    | M (ITS)                                                                    | 27             |

| 3.1<br>3.2               |                    | Overviewndom Logic Implementation                                          | 27<br>29       |

| 3.3<br>3.4               | Selection          | on of a Microprocessorrocessor-Based ITS                                   | 30             |

|                          | Using a            | UART                                                                       | 33             |

| 3.5                      | Using S            | rocessor-Based ITS<br>Serial I/O                                           | 38             |

| 3.6                      |                    | Features of the cs 2650                                                    | 42             |

|                          | Quiz fo            | or Chapter IIIrs to Quiz                                                   | 45<br>46       |

|                          | Bibliog            | graphy                                                                     | 47             |

|                          | Glossa             | ry of Microprocessor Terms                                                 | 49             |

| Арр                      | endix A            | Signetics 2650 Microprocessor Specifications                               | 59             |

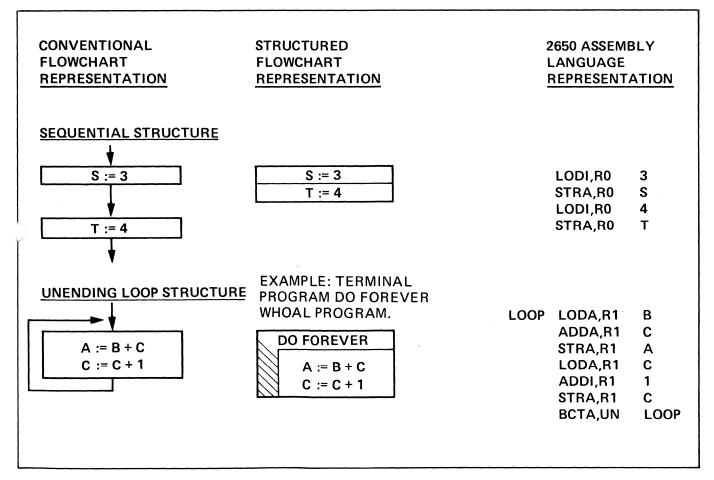

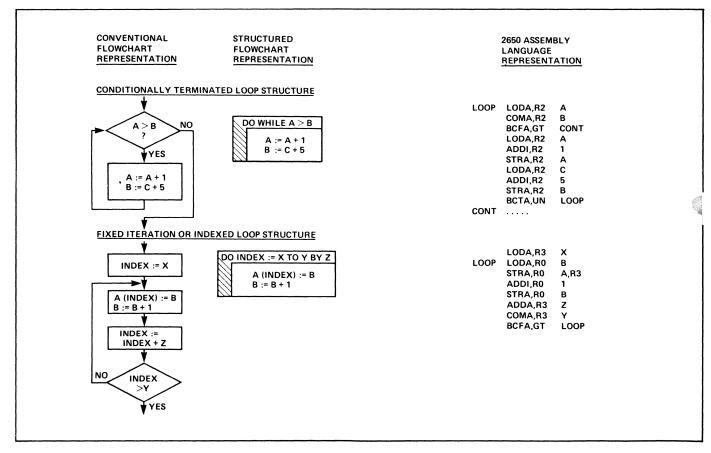

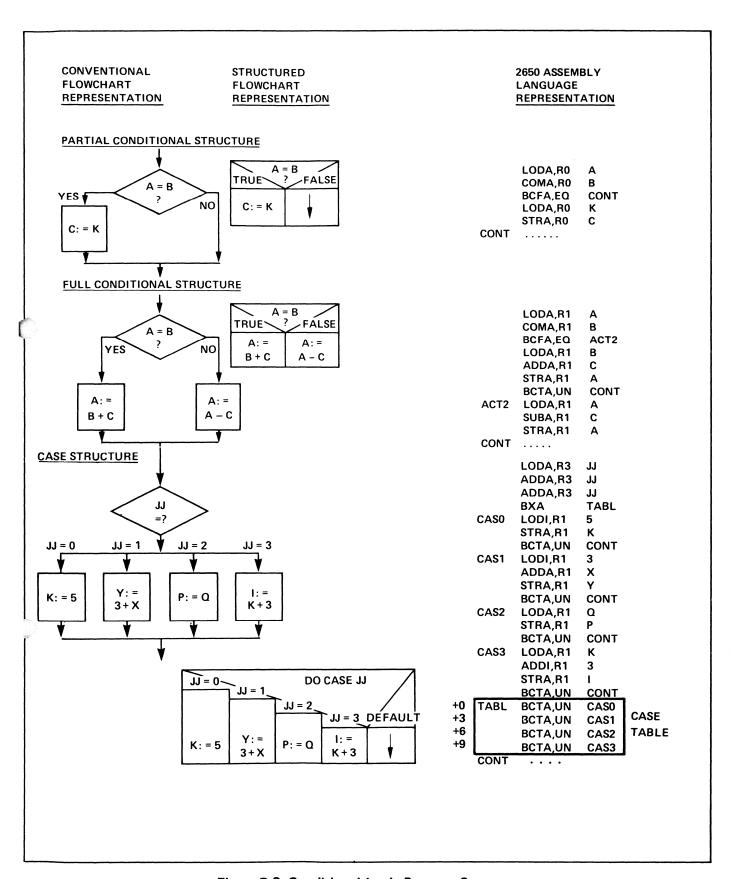

| Арр                      | endix B            | Microcomputer Programming Techniques with Illustrations                    | 63             |

| Арр                      | endix C            | Intelligent Typewriter Program Listing                                     | 71             |

# PREFACE: WHAT THIS BOOK IS ABOUT

This text is short because it has a singular objective: to teach you what a microcomputer is and how you (or your staff) can design with it. We've put a bibliography in the back if you want to know more about how and why microcomputers are revolutionizing electronics, what new applications have opened up, how to compare microcomputers, etc.

The approach of the book is very simple. A real-life design problem (currently in volume production) is posed and solved with a real-life microprocessor, the Signetics 2650.

To help you learn from the text, we've incorporated several features: key words are identified in both the text and separate glossary. There are two quizzes and, finally, the text is extensively illustrated.

The book can be read in about four hours — an easy investment for learning about what many say is the most important technological innovation of this decade.

### I. INTRODUCTION

With the introduction of a class of electronic components called microprocessors, the hardware implementation of physical systems, governing a wide range of applications has undergone a radical change. The objective of this book is to assist electronic system engineers, managers and other creative individuals to reorient their system implementation methodology to take advantage of the exciting possibilities offered by this novel component. This process of reorientation is accomplished by taking the reader through the main steps of a specific electronic design problem; namely, the design of an intelligent typewriter system (ITS), using a microcomputer. This particular design example was selected because: (1) the system hardware configuration is usable in a number of other applications with similar serial input/output requirements, and (2) the hardware components, mounted on a PC card, are available for evaulation and demonstration.

Before we begin, note that we are using two words, microprocessor and microcomputer.

MICROPROCESSOR

The microprocessor is a device which performs arithmetic, control, and logical operations.

MICROCOMPUTER

The microcomputer, in turn, is a collection of devices that includes a microprocessor, memory, and associated interface circuits to communicate with the "outside world." This essential distinction will become clearer as we progress.

### 1.1 System Development Procedure

Using the microprocessor as a key system component, the system designer can significantly reduce the hardware component count and, therefore, production costs. But during the prototype development phase, he needs to carefully design the microcomputer software, and the hardware interface between the microcomputer and the "outside world."

The fundamental trade-off that must be foremost in the mind of the designer is: How can I configure the system so as to minimize the component count and hardware complexity by performing more functions within the microcomputer, without any significant degradation in overall system performance (or response)?

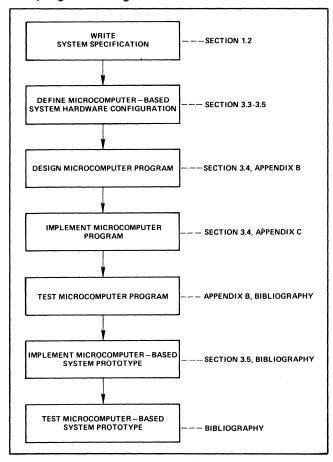

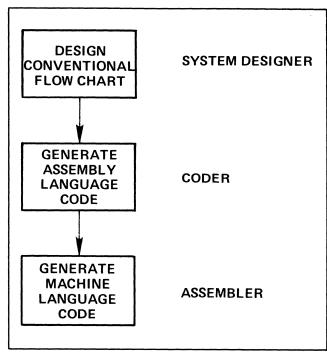

The sequence of procedural steps to be followed in the development of a hardware prototype system are familiar to most electronic system designers and managers. For the sake of completeness, this familiar sequence is presented in Figure 1.1 for a microcomputer-based prototype system. The first block requires the designer or the manager to write a detailed description of the functions the system is to perform; Section 1.2 will document the functional specification for the aforementioned ITS.

On the basis of this specification, a suitable system hardware configuration must be defined to (1) meet the interface requirements between the microcomputer and the "outside world" and (2) provide adequate capability within the microcomputer to meet the functional specification. In general, for a particular microprocessor, some ingenuity is required to accomplish these requirements economically. (These new components, therefore, do not supercede the need for clever engineers.) The definition of a suitable microcomputer hardware configuration for the ITS System is elaborated in Chapter III.

PROGRAM

The next step is to design the microcomputer program. By program is meant the "customized" sequencing of logical, arithmetic and control operations of the microprocessor to meet the desired functional specification. The system designer begins by breaking down the functions required into a set of elementary procedural steps arranged in a systematic and clearly defined manner by a suitable program description; additional details concerning this facet of system design are described in Appendix B.

The microcomputer program designed in the previous step is then implemented and tested in the two following blocks of Figure 1.1. The ease with which the program is implemented and tested, largely depends on the usage of proper structuring techniques during the program design process in the previous step. Programming methodologies that result in "well-structured" programs are presented in Appendix B. Then, a microcomputer-based hardware prototype system is implemented, incorporating the previously tested microcomputer program.

Successful testing of this prototype system completes the prototype development.

This book is organized as follows: In the following section, the intelligent typewriter system (ITS)'s design problem is specified. Since the design involves usage of a microcomputer, basic computer concepts are reviewed in chapter II, this material can be skipped by the computer specialists. Chapter III describes the design of the ITS, using the Signetics 2650 microprocessor. Additional microcomputer concepts and features, not required by the ITS but useful in other applications, are also described in chapter III. Figure 1.1 relates the discussions in the various sections to the typical development process.

The main text is followed by a selected bibliography of microcomputer literature and a glossary of commonly occurring terms. Appendix A presents the Signetics 2650 Microprocessor instruction set and electrical specifications. Appendix B describes alternative methodologies for microcomputer programming. Appendix C presents the ITS program listing.

Figure 1.1 Prototype Development Procedure

## 1.2 The Design Problem: An Intelligent Typewriter System (ITS)

The overall design problem is to implement an intelligent typewriter system (i.e., text generating system) which outputs a "previously specified" text, with certain blank spaces that can be filled in by the user, to "customize" the text (e.g., a form letter with the name, age, and social security number of the individual to whom it is to be sent). The input medium for the "previously specified" text is to be the familiar typewriter keyboard. The output medium is to be the typewriter printing mechanism. Moreover, control characters need to be implemented into the system to allow insertion of unique characters at locations identified during text generation. Additional control characters will be required to provide an edit (i.e., erasure of the previous character entered) and system reset capability.

The above functional specification of the intelligent typewriter system (ITS) expressed in commonly used English language is reworded in more precise technical terminology in chapter III. In this section certain hardware constraints are imposed and the functional usage of the various control characters is defined. Then, in chapter III (after a review of microcomputer fundamentals in chapter II), the hardware and software configuration details, as outlined in Figure 1.1 are generated. A listing of the software portion of the ITS is included in Appendix C.

For the typewriter mechanism, we will employ a teletype (TTY) terminal. We will use this device for two reasons. First, a microcomputer must always employ an input/output (I/O) device or devices. The TTY can perform all the I/O functions for our application. Second, as a microcomputer system designer, you will ultimately have to employ a TTY or similar terminal in developing the microcomputer system itself. An understanding of the ITS/Teletype interface gives you a head-start in understanding these terminals and their operation.

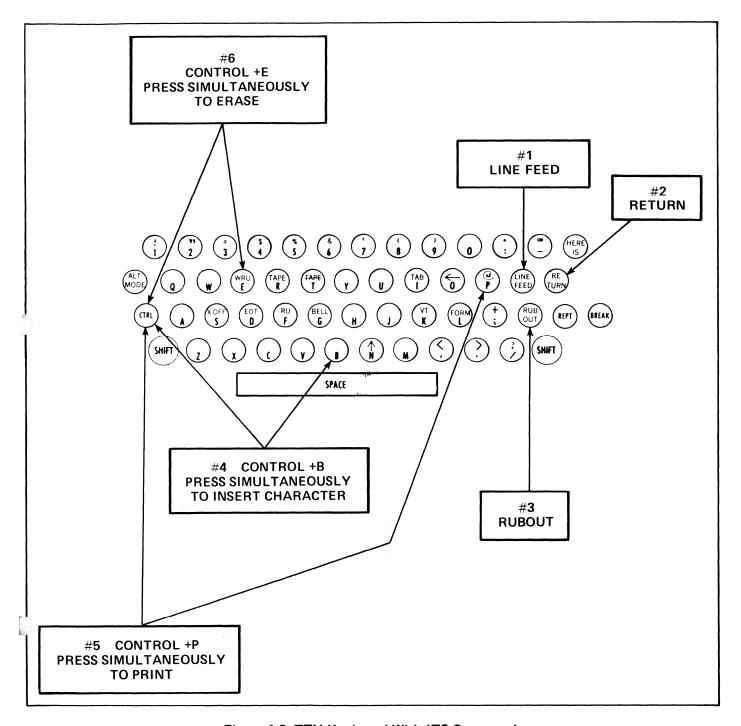

Operation of the TTY is very similar to operation of a typewriter with the exception that the TTY has some additional keys. Figure 1.2 shows the TTY keyboard. The keyboard includes the familiar alphanumeric keys found on a conventional typewriter. In addition to these, there are several control keys. These are described in terms of operation of the ITS as follows:

Figure 1.2 TTY Keyboard With ITS Commands

- 1. The LINE FEED key advances the paper, on which the TTY is printing, by one line.

- 2. The TTY printing mechanism moves from left to right while printing. The RETURN key moves the printing mechanism to the left hand margin.

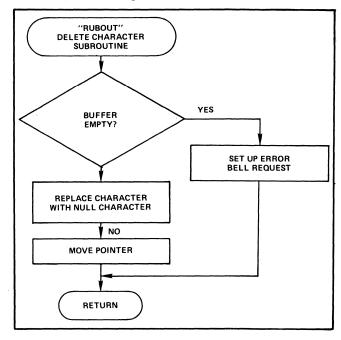

- Recall that the user will be typing into the microcomputer memory. (This will include letters,

- numerals, line feeds, and returns.) The RUBOUT key will be used to delete from memory the last typed character or control key. Additional preceding characters can be deleted by continuing to press the RUBOUT key. RUBOUT will affect the editing function of the ITS.

- 4. The IDS feature for producing form letters will be acheived using the following set of controls.

When the user reaches a point in the letter where unique information is to be inserted, he will simultaneously depress the CTRL key and character B. (We will refer to this combination as CONTROL + B.) This will cause the material written back from memory to stop so that the unique information may be typed in by the user. After the user has typed in the unique information, he can resume the typing from memory by depressing CONTROL + C.

- 5. We will provide the user with a command CONTROL + 'P which will initiate printout from microcomputer memory.

- 6. Finally, the entire storage of the ITS can be erased by depressing CONTROL + E.

The TTY terminal has a bell which can be operated

on command from the microcomputer. We will ring the bell when the user:

- 1. Attempts to store more data characters than the ITS storage will permit. Let us limit this to 250 characters.

- 2. Tries to read an empty memory.

- 3. Attempts to delete more characters than exist in storage.

- 4. Attempts to continue printing after the contents of memory have been printed out.

The ITS system is now specified. Before describing the actual microcomputer design, we must first review some computer concepts. This is the subject of the next chapter.

### II. MICROCOMPUTER BASICS

### 2.1 Introduction

This chapter develops the fundamental concepts one needs to understand and use microcomputers. The basic approach of the chapter is to develop the structure (i.e., architecture) and operation of a practical microprocessor. We begin by describing a very simple device, a hand calculator, that adds binary numbers. In the next section, the device is redesigned to operate automatically—becoming, in fact, a very primitive microcomputer. In subsequent sections, additional refinements are added until the complete microcomputer system is defined.

### 2.2 A Binary Hand Calculator

Everyone has operated a (decimal) hand calculator. Numbers are entered on a keyboard, operations are performed (+, ÷, =, etc.), and results are displayed. As it turns out, the operations one goes through in operating a hand calculator match very closely with what happens in a microcomputer. To show this correspondence, let's first design a very simple hand calculator, one that works with binary numbers. In fact, let's restrict operation of the device to the following: we can enter two numbers (in binary) and output the sum, i.e., out calculator will be a binary parallel adder. (We can, of course, do this with one chip, but our purpose here is to ultimately evolve to a microcomputer.)

In a real calculator design, one must first ask, how many digits should be used? The selection comes by trading off desired precision with circuit complexity (i.e., the more digits, the more complex the calculator).

BIT

We will use 8 binary digits (bits) since we will be ultimately describing an 8-bit microcomputer. Hence each number we wish to add will be represented by 8 bits as will their sum.

BYTE

We will refer to this group of 8 bits as a byte. The following examples show decimal addition along with the corresponding addition in binary.

Table 3.1 Addition Example

| Decimal     | Binary Equivalent |

|-------------|-------------------|

| 11          | 00001011          |

| <u>+ 6</u>  | +00000110         |

| 17          | 00010001          |

| 130         | 10000010          |

| <u>+ 15</u> | +00001111         |

| 145         | 10010001          |

Note that we use 8 bits or one byte to represent each number in binary.

We can now move on to describing the design of the binary calculator. In doing so, it is necessary to introduce the reader to a logic device which will be the heart not only of the calculator at hand, but also of the microcomputer.

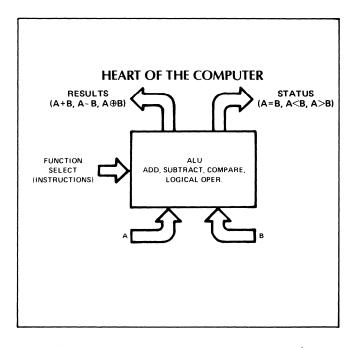

ALU

This device is called an arithmetic-logic unit (ALU) and is shown in Figure 2.1. As the figure suggests, the ALU takes inputs A and B and performs functions (add, subtract, compare, etc.) based on a function select input and outputs a result. (We will be discussing the status output later.)

Figure 2.1 Arithmetic Logic Unit (ALU)

For our binary calculator, we will be concerned only with the addition feature of the ALU. Inputs A and B will represent the two one-byte numbers to be added and the result (A + B) will also be one byte (i.e., the inputs A + B and the output in the figure actually consists of eight parallel lines.) We will assume that the function select in the figure has whatever is required to effect the add function of the ALU.

**OPERANDS**

Finally, since the ALU will be performing an (add) operation on A and B, we will call A and B operands.

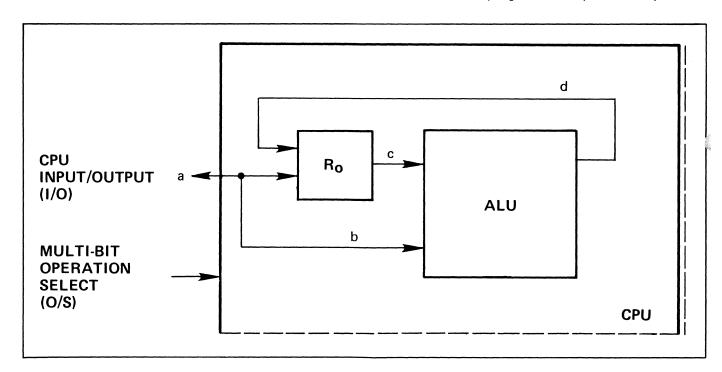

We could, at this point, complete the design of the binary calculator using 16 switches (8 Single Pole-Double Throw switches connected to 0 and 5 volts for each input byte) and 8 lamps driven from the buffered ALU output. However, we ultimately intend to convert this calculator into a microcomputer. For this reason, we will complicate the calculator design by supplementing the ALU with an 8-bit register R<sub>0</sub> as shown in Figure 2.2.

CPU

What results is called a central processing unit (CPU) and functions as follows:

INPUT

Looking outside the CPU, a byte can be an **input** (i.e., fed into) the CPU or

OUTPUT

output (i.e., driven out) depending upon an operation select which can have one of several states.

That is, input and output share the same set of lines, since the data flows in both directions—in and out. Looking inside the CPU, we see R<sub>0</sub> connected to both the input/output as well as the ALU. These lines are one byte wide.

I/O

It should be noted that the interconnections as shown are not actual electrical connections but rather a composite of all possible signal paths among R<sub>0</sub>, the ALU, and the INPUT/OUTPUT (I/O) terminal of the CPU. We will shortly discuss these signal paths.

Inputs to the ALU are the operand inputs (e.g., A and B in Figure 2.1) to the ALU itself is not shown for it is driven by logic whose input is the operation

Figure 2.2 Central Processing Unit (CPU)

select input to the CPU. As indicated above, the CPU interconnections shown in Figure 2.2 represents a composite of signal paths. The actual paths themselves are governed by the state of the operation select input. These individual paths can be visualized by considering the operation of the CPU. For our calculator application, the CPU has three operating modes:

MODE 1: A byte can be **input** directly into R<sub>0</sub>. That is, the 8 bits in R<sub>0</sub> will be set to whatever 8 bits are on the input. (a). In this mode paths to and from the ALU (b, c, and d) are inactive. (Logic gates enabled and disabled by the signals on the OPERATION SELECT input perform this function.)

MODE 2: The ALU will take the byte on the input a/b and the byte in R<sub>0</sub> (c) and sequentially perform the binary sum placing the result in R<sub>0</sub> (through path d). In this case, the path between input and R<sub>0</sub> is inactive. Note also that the prior contents of R<sub>0</sub> are destroyed.

MODE 3: The contents of R<sub>0</sub> are fed to the output (a). Here, all ALU paths are inactive. Also, the contents of R<sub>0</sub> are unaltered.

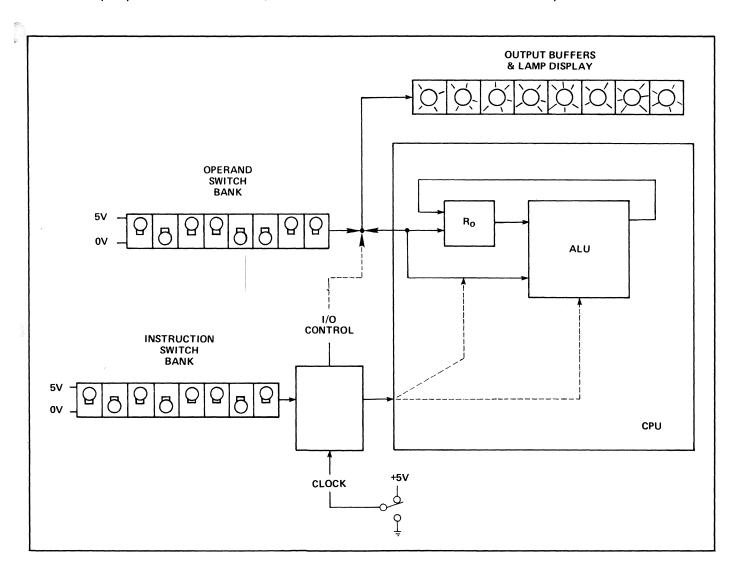

It is now a simple matter to construct a binary calculator. Figure 2.3 shows a possible implementation using switch banks and lamps. Referring to the figure, we will be sequentially putting the numbers to be added into the operand switch bank. The

Figure 2.3 Binary Calculator

resultant output (A + B) will be displayed on the output lamp display. (Note again that input and output paths are shown as a composite; the actual path employed will be controlled by additional logic not shown.) We can select I/O paths and select the CPU operating mode using an 8 bit\* (i.e., one byte long) instruction switch bank.

INSTRUCTION

Here we use the word instruction in the sense that the setting of the eight switches will "instruct" the CPU and other logic what to do.

CLOCK

Since we will be sequentially setting switches and operating the CPU, it will be necessary to provide the system with clock pulses as shown. The binary calculator is now designed.

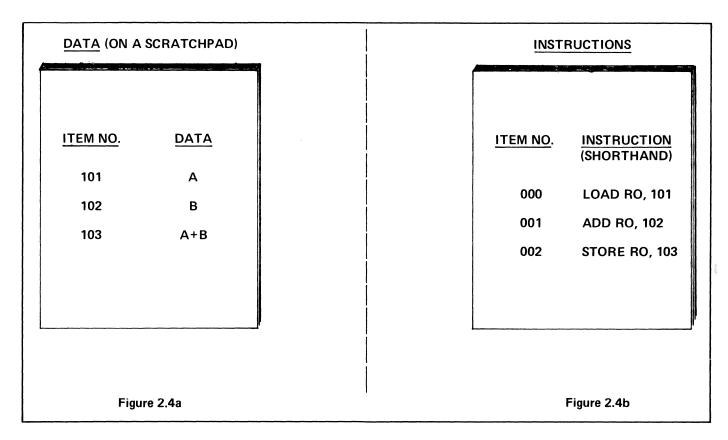

We can turn now to operation of the system. Let's suppose that we want the binary sum of operands A and B (i.e., we want A + B). To be orderly, let's put both the operands A and B and the result (when we get it) on a scratch pad as in Figure 2.4a.

DATA

We will refer to A, B, and A + B as data, i.e., binary numbers that are the object of the calculation.

To be orderly, let's itemize the data using numbers 101, 102, 103 as shown. In similar fashion, we can list the instructions that have to be performed on another piece of paper as shown in Figure 2.4b. Each instruction as shown is in a shorthand notation and represents one or more unique 8-bit bytes which will be placed in the instruction switch bank and clocked into the system. These binary instructions will be discussed in a later section; the shorthand designation will be discussed shortly. Note

Figure 2.4 Data and Instructions

<sup>\*</sup>At this point, the use of an 8 bit "instruction" was somewhat arbitrary. To perform the add operation, fewer bits are actually required. However, as we will see later, there is a relationship between the length of the data word A, B, etc. and the instruction in a real microcomputer.

that like the data, the instructions are itemized with decimal numbers 000, 001, 002. Note also that data and instructions have different item numbers.

The calculator can now be operated by writing data A and B next to item numbers 101 and 102 and executing the instructions sequentially starting with item 000 as follows:

- 1. Instruction Item 000: Put the data in data item 101 in the operand switch bank and place (i.e., load) it into register R<sub>0</sub>. A now resides in R<sub>0</sub>.

- 2. Instruction Item 001: Put the data in data item 102 into the operand switch bank. Add this value to the contents of  $R_0$  (A) and place the result in  $R_0$ . A + B now resides in  $R_0$ .

- 3. Instruction Item 002: Output the contents of R<sub>0</sub> (A + B) to the lamp display and place (i.e., store) the value at data item 103.

Again, note that in actuality each instruction consists of one or more eight-bit bytes set into the instruction switch bank. (As mentioned, these will be discussed in greater detail later on.) For the time bing, we will refer to these instructions by the English equivalents shown in Figure 2.4b.

LOAD: puts CPU input into  $R_0$ .

ADD: adds CPU input to contents of  $R_0$  and places the result into  $R_0$ .

STORE: places the contents of  $R_0$  on the data scratch pad.

Let's move on now to automating the calculator and in the process, develop a basic minicomputer.

### 2.3 An Automatic Calculator

In this section, we will modify the calculator of Figure 2.3 such that it will operate automatically. In doing so, it is clear that we must mechanize the process of getting both the data and instruction lists of Figure 2.4 in and out of the hardware. The key to this is a new hardware element: **Memory**.

MEMORY

MEMORY

For our purposes, we will describe memory as a device which contains 8-bit bytes. In particular, these 8-bit bytes comprise the data and instruction bytes of Figure 2.4.

**DATA MEMORY INSTRUCTION MEMORY** READ/WRITE CONTENTS **ADDRESS** COMMAND **CONTENTS (8 BITS)** (8 BITS) (15 BITS) (CAN BE CAN BE **ADDRESS READ ONLY)** READ (15 BITS) OR STORED Figure 2.5a Hardware: Random Access Memory (RAM) Figure 2.5b Hardware: Read Only Memory (ROM)

Figure 2.5 Memory

CONTENTS

We will refer to these bytes as memory contents. Since these bytes are stored in hardware, the question naturally arises—how does the remaining hardware know which byte is which? and where in memory they are located.

**ADDRESS**

This question is resolved by giving each byte an address.

The address here corresponds exactly with the data item and instruction item numbers shown in the lists in Figure 2.4 (e.g., 101, 102, 001, 002, etc.). For the microcomputer system we are developing, we will use a 15-bit address. (That is, in our system, we could use a memory having as many as 32,768 unique contents.)

Finally, just as we had a data list and instruction list in Figure 2.4, we will employ a data memory and instruction memory. These are depicted conceptually in Figure 2.5.

DATA MEMORY

For the data memory, we can either output (i.e., read) the contents of each binary address or input (i.e., store) a byte which will become contents at that address.

We can read or store depending upon whether the read/write command (Figure 2.5a) is high or low. It should be noted here that when data are read, the contents are undisturbed; however, when data are stored, the original contents are lost. Figure 2.5b shows the instruction memory.

INSTRUCTION MEMORY

Instruction memory will only be read. (Recall in the lists of Figure 2.4 that we read A and B off the data list and stored the sum A + B; we only read the instruction list.)

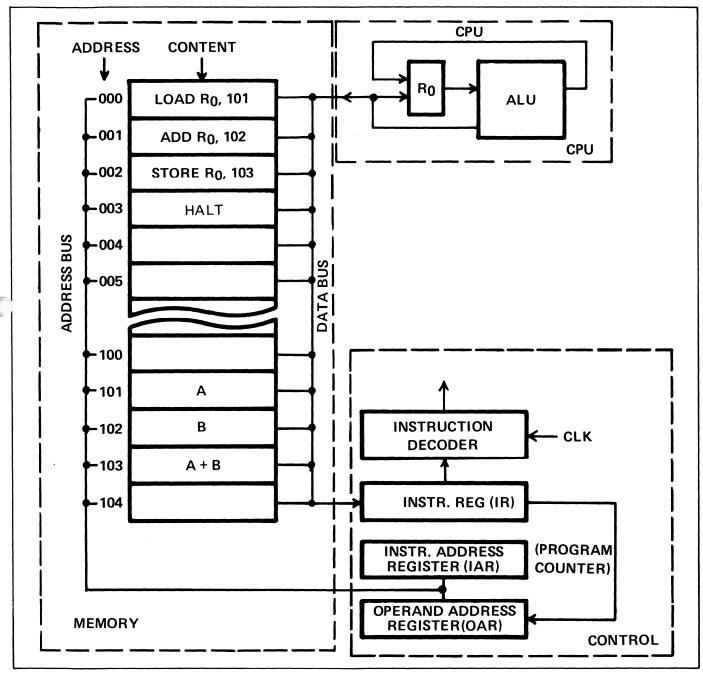

At this point, let's now interface the data and instruction memories with the calculator hardware of Figure 2.3. We will be able to read data memory contents directly into  $R_0$ . Hence, we can eliminate the operand switch bank. In a similar fashion, let's replace the instruction switch bank with an 8-bit register into which we can place the contents of the instruction memory.

INSTRUCTION REGISTER

We will call this register an instruction register (IR). It will serve the same purpose in the automatic calculator that the instruction switch bank served in the hand calculator.

At this point, we now have data memory contents feeding  $R_0$  and the instruction memory contents feeding an instruction register. We must finally "address" data memory and instruction memory in order to determine which data goes into  $R_0$  and which instructions go into IR.

OPERAND ADDRESS REGISTER We will add two new registers for this purpose: an operand address register (OAR) for addressing data (or operand) memory

INSTRUCTION ADDRESS REGISTER

and an instruction address register (IAR) for addressing instruction memory. These registers will have 15 bits to match the number of address bits.

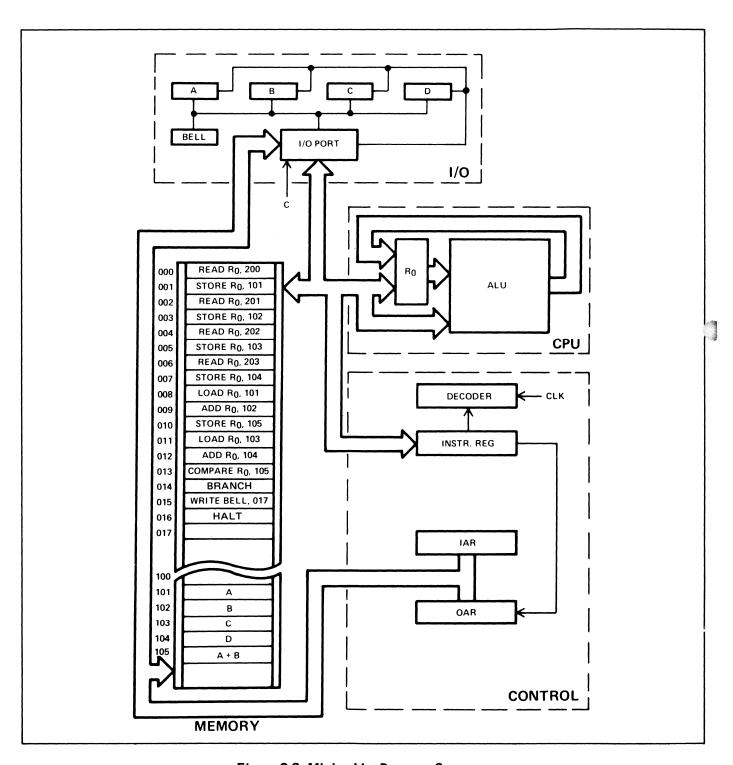

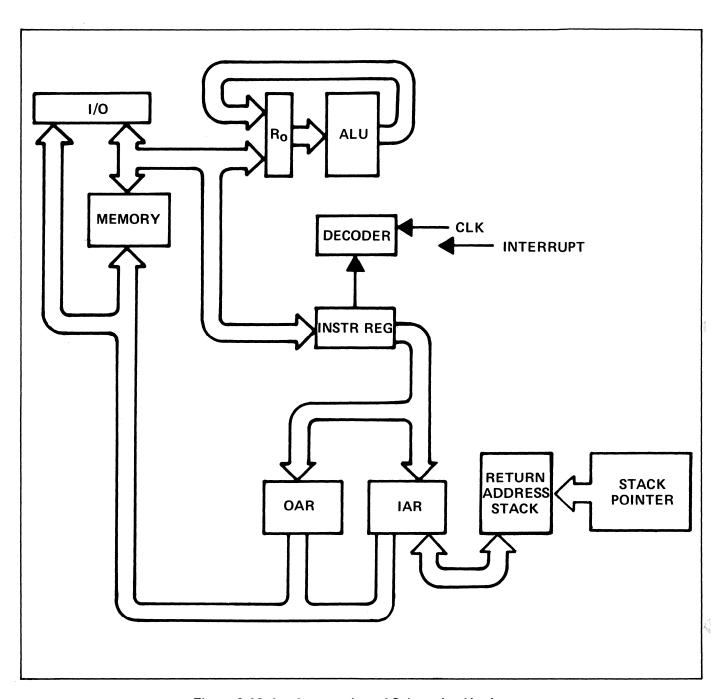

Memory and foregoing registers are shown interconnected in Figure 2.6. Note first that the output lamps have been removed since we can now store R<sub>0</sub> directly into data memory. Studying the figure, we see that the automatic calculator has three basic blocks: (1) CPU, (2) Memory, and (3) Control.

MICROPROCESSOR

It should be noted here that CPU and Control Sections comprise a microprocessor.

**MICROCOMPUTER**

A microcomputer on the other hand consists of a microprocessor, memory, and I/O. The CPU is unchanged from previous examples.

The memory block depicts both instruction memory contents (upper half of memory block) and data memory contents (lower half). Associated with each content is a unique address. Note that addresses and contents correspond exactly with the data and instruction lists we made for the hand calculator (Figure 2.4).

BUS

Addresses are selected by activating an address line or addres bus which as noted earlier is 15 bits wide.

Figure 2.6 Automatic Calculator

Memory contents can be individually placed on an 8-bit bidirectional data line

or data bus; in the case of the data memory, data can be both placed onto and from the data bus.

Note that the data bus as shown is a composite. Only one content will be on the data bus at a time.

The control unit contains the 8-bit instruction register (IR) and the 15-bit instruction address register (IAR) and 15-bit operand address register (OAR). Since the instructions are in numerical order, the instruction address register is incremented by one after each addressing of instruction memory. For this reason, the IAR is sometimes called a program counter. The final item in the control block is the instruction decoder. The decoder uses the contents of the IR as input to control other parts of the

system (CPU operation select, memory read/write, signal path select, etc.). Note in the figure that both the IAR and OAR are on the address bus. In actuality, only one register at a time is on the bus. Finally, note the signal path between the IR and OAR. This path is shown since in the actual microcomputer the contents of the OAR are governed by the IR. We will discuss this point in more detail in Section 2.10.

At this point, let us now discuss the operation of the automatic calculator. Refer to Figure 2.6. We will assume that the instructions are in instruction memory as shown. A and B are in data memory. The system will compute A + B and store the result in data memory as follows:

- 1. The instruction address register will be initially set to a value corresponding to memory location 000. This will cause contents of location 000 (Load  $R_0$ , 101) to be placed on the data bus and into the instruction register. The instruction itself specifies the loading of R<sub>0</sub> with data stored at address 101; hence, the operand address register will take on a value corresponding to address 101. (This is accomplished by transferring a portion of the instruction-namely, "101" to the OAR. This is accomplished automatically when the Instruction Decode circuitry decodes the instruction.) The instruction decoder will then cause the system to place the contents of OAR on the Address Bus which, in turn, puts A on the data bus and finally into R<sub>0</sub>. The instruction address register will automatically increase by one to 001. A is now in  $R_0$ .

- 2. With the instruction address register at value 001, the instruction ADD R<sub>0</sub>, 102 will be put on the data bus and placed into the instruction register. The operand address register will take on value 102 causing B to appear on the data bus where it will be input to the (lower) ALU input. The ALU will add what is in R<sub>0</sub> and B and return the result to R<sub>0</sub>. This again is caused by signals from the instruction decoder which is looking at the ADD instruction. The instruction address register will again increment by one to address 102. The sum A + B is now in R<sub>0</sub>.

- 3. The instruction address register will put instruction STORE  $R_0$ , 103 on the data bus and into the instruction register. The operand address register will take on value 103 and the data in  $R_0$  (A + B) will be stored in data memory location 103.

HALT

Note the addition of a **HALT** instruction at memory address 003.

HALT stops excution of instructions. (Without a HALT, the instruction register would be loaded with unknown contents that could cause the system to behave unpredictably, e.g., storing something other than A + B at data address 103.) The system will accordingly have behaved as an automatic calculator. The system is, in fact, a microcomputer. One element is lacking, however: communication with the outside world. This aspect is covered by an example in the following section.

### 2.4 A More Practical Example: Mixing Vat

Let us, at this point, leave the calculator problem behind and look at a somewhat more practical problem.

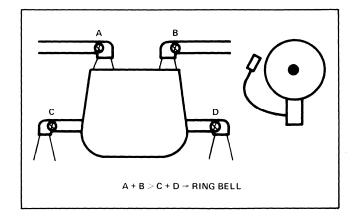

Figure 2.7 depicts a mixing vat having two pipes placing material into the top of the vat and two pipes extracting material from the bottom of the vat. We will monitor flow rates in all pipes (A and B at the top, C and D at the bottom as shown). We will use the microcomputer system to calculate total flowrate into the vat (A + B) and total flowrate out (C + D). If, at any time, flowrate into the vat exceeds flowrate out [i.e., (A + B) > (C + D)] we will cause a bell to ring.

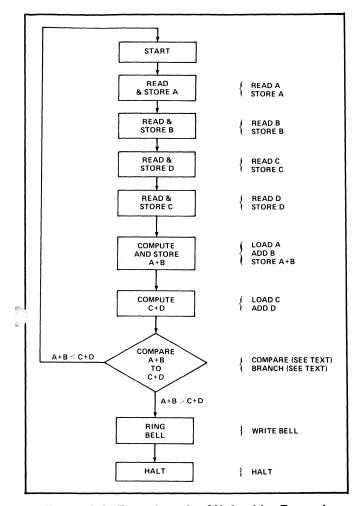

Looking at the above requirements, the microcomputer system must have instructions that will read in the flowrates, perform the appropriate sums, and make a comparison. A convenient technique for obtaining these instructions is to first diagram the sequence of individual steps in a flowchart as shown in Figure 2.8.

Figure 2.7 Mixing Vat Example

Figure 2.8 Flowchart for Mixing Vat Example

FLOWCHART

Instructions can then be written from the flowchart as shown.

Our microcomputer system can perform this task as shown in Figure 2.9. The CPU, Control, and Memory Sections are the same. Two things, however, have changed:

- The data bus and address bus go out to an input/ output (I/O) block containing the flowrate meters and the bell.

- 2. We have more instructions than in the previous example.

The I/O block comprises external logic (I/O port) connected to the four flowmeters and the bell. This logic is designed to selectively place A, B, C, D, or the bell on the data bus as a function of inputs from the address bus. Note here that the address bus is being used in conjunction with a control line "C" (discussed in more detail in Section 2.10) to

not only select data and instruction memory contents but to also select devices outside of the system. For this reason, we must select "I/O addresses" distinct from instruction and data addresses. The I/O addresses for the figure are tabulated as follows:

Table 2.2 I/O Addresses

| I/O Address | Item on Data Bus |

|-------------|------------------|

| 017         | Bell             |

| 200         | Α                |

| 201         | В                |

| 202         | С                |

| 203         | D                |

Look now at the instructions. From the foregoing, it should be apparent that all the READ instructions are accessing the flowmeter data and not memory. The reader is already familiar with READ, STORE, and LOAD instructions and should at this point be able to trace through the microcomputer operation through instruction address 012. (Try it!) After execution of instruction 012, we have (A + B) at data memory address 105 and register  $R_0$  contains (C + D).

These instructions at 013 (COMPARE  $R_0$ , 105) and 014 (BRANCH 000) are new. Moreover, they are interrelated (in a manner that will be explained in Section 2.9). Basically, these instructions work as follows.

BRANCH

The BRANCH 000 causes the instruction address register to be reset to 000 (i.e., BRANCH XYZ resets the IAR to XYZ).

Instructions beginning at 000 are then repeated. The BRANCH instructions, however, is executed as a result of what happens with the COMPARE instruction as follows.

COMPARE

The COMPARE  $R_0$ , 105 instruction compares the magnitude of the contents of  $R_0$  (C + D) with the contents of memory address 105 (A + B).

If the contents of  $R_0$  are greater than (i.e., flow out is greater than flow in) the contents at 105 the BRANCH instruction is executed. Otherwise, the BRANCH instruction is ignored and the next instruction (WRITE) is executed. The WRITE BELL, 017 instruction is self-explanatory.

Figure 2.9 Mixing Vat Program Sequence

The reader should now see that the system of Figure 2.8 will be continuously computing (A + B) and (C + D) and comparing magnitudes until (A + B) > (C + D), at which point, the bell will ring.

This example introduces two new things that can

happen in microcomputer systems:

- 1. The system can make *decisions* (compare then BRANCH or don't BRANCH).

- 2. The sequence of instructions can be changed (e.g., due to BRANCH) and repeated.

Moreover, the example begins to illustrate the most important point in this book: EXCEPTING FOR THE I/O, THE MICROCOMPUTER HARDWARE IS FIXED; THE ACTUAL SYSTEM DESIGN LIES MAINLY IN DESIGNING THE SEQUENCE OF INSTRUCTIONS.

This point becomes more obvious as we consider some further instructions in the next section.

### 2.5 A More Powerful Microcomputer

PROGRAMMING

As stated in the previous section, design with microcomputers will principally comprise designing a sequence of instructions or, to define a new term, programming.

Consequently, we can make our microcomputer in Figure 2.9 a more powerful device by increasing the number and diversity of instructions.

We can at this point very easily introduce several new instructions. Recall that the microcomputer CPU was developed using an arithmetic logic unit ALU. So far, we have discussed use of the ALU only for addition. Referring back to Figure 2.1, it should be obvious that other operations can be performed. For example, we can SUBTRACT operands (A - B). Additionally, logical operations can be performed.

AND

For example, we can AND operands A and B.

Recall that operands A and B are 8-bit bytes by "and-ing" corresponding bits giving an 8-bit byte as a result (A • B) as in the following example:

Table 2.3 AND Operation Example

| ALU Input |          | ALU Output |

|-----------|----------|------------|

| Α         | В        | A • B      |

| 10101100  | 11001010 | 10001000   |

Note also that the 8-bit operands need not be binary numbers. In fact, the operands can represent data characters (e.g., as in the intelligent typewriter system to be discussed later), codes, logic states, etc.

INCLUSIVE OR

**EXCLUSIVE OR**

We can, in similar fashion to the above, develop other logical instructions such as "INCLUSIVE OR" and "EX-CLUSIVE OR":

Table 2.4 OR Function Example

| FUNCTION                     | ALU INPUT            |   | ALU OUTPUT           |

|------------------------------|----------------------|---|----------------------|

|                              | Α                    | В | A + B                |

| INCLUSIVE OR<br>EXCLUSIVE OR | 10101100<br>10101100 |   | 11101110<br>01100110 |

These instructions are shown in Table 2.6 which includes instructions discussed in previous sections.

ROTATE

Also included are **ROTATE** instructions (ROTATE LEFT and ROTATE RIGHT).

These instructions move the bits in register  $R_0$  one bit to the left or right as described in the table and as indicated in the following.

Table 2.5 ROTATE Instruction Example

|              | BEFORE ROTATE | AFTER ROTATE |

|--------------|---------------|--------------|

| ROTATE RIGHT | 11010101      | 11101010     |

| ROTATE LEFT  | 11010101      | 10101011     |

It should be clear that, as a group, the instructions shown in Table 2.6 make the basic microcomputer hardware we've developed very flexible in terms of what can be performed on the outside world. By now, the reader has probably been wondering. "How fast are these instructions performed?" As it turns out, time to execute each instruction varies from instruction to instruction. On the average, however, instructions are performed in about 7 microseconds. In the previous examples, it would, therefore, take about 21 microseconds for the automatic calculator to sum and store results; each mixing vat computation would be done in about 110 microseconds.

Instructions have been discussed so far by their English equivalents (READ, ADD, STORE, etc.). As we know, the instructions, themselves, are made up of one or more bytes that are loaded into the instruction register. We discuss this in the next section.

**Table 2.6 Microcomputer Instruction List Example**

| INSTRUCTION         | FUNCTION                                                                                                |

|---------------------|---------------------------------------------------------------------------------------------------------|

| LOAD R <sub>0</sub> | Loads R <sub>0</sub>                                                                                    |

| STORE               | Places the contents of R <sub>0</sub> into memory                                                       |

| ADD                 | Adds to $R_0$ what is on data bus and puts result in $R_0$                                              |

| SUBTRACT            | Subtracts what is on data bus from $R_0$ and puts result in $R_0$                                       |

| AND                 | "Ands" what is on data bus with $R_0$ and puts result in $R_0$                                          |

| INCLUSIVE OR        | Performs ''Inclusive OR'' between data bus contents and R <sub>0</sub> putting result in R <sub>0</sub> |

| EXCLUSIVE OR        | Performs "Exclusive OR" between data bus contents and $R_0$ putting result in $R_0$                     |

| COMPARE             | Compares data memory content with R <sub>0</sub> as prerequisite to branch                              |

| ROTATE RIGHT        | Shifts bits in $R_0$ one bit to right. Least significant bit moves to most significant bit position     |

| ROTATE LEFT         | Shifts bits in $R_0$ one bit to left. Most significant bit moves to least significant bit position      |

| BRANCH              | Causes instructions to begin execution at another instruction address                                   |

| WRITE               | Places contents of R <sub>0</sub> onto data bus                                                         |

| READ                | Places contents of memory (or I/O) into R <sub>0</sub>                                                  |

| HALT                | Stops instruction execution                                                                             |

### 2.6 Binary Instructions

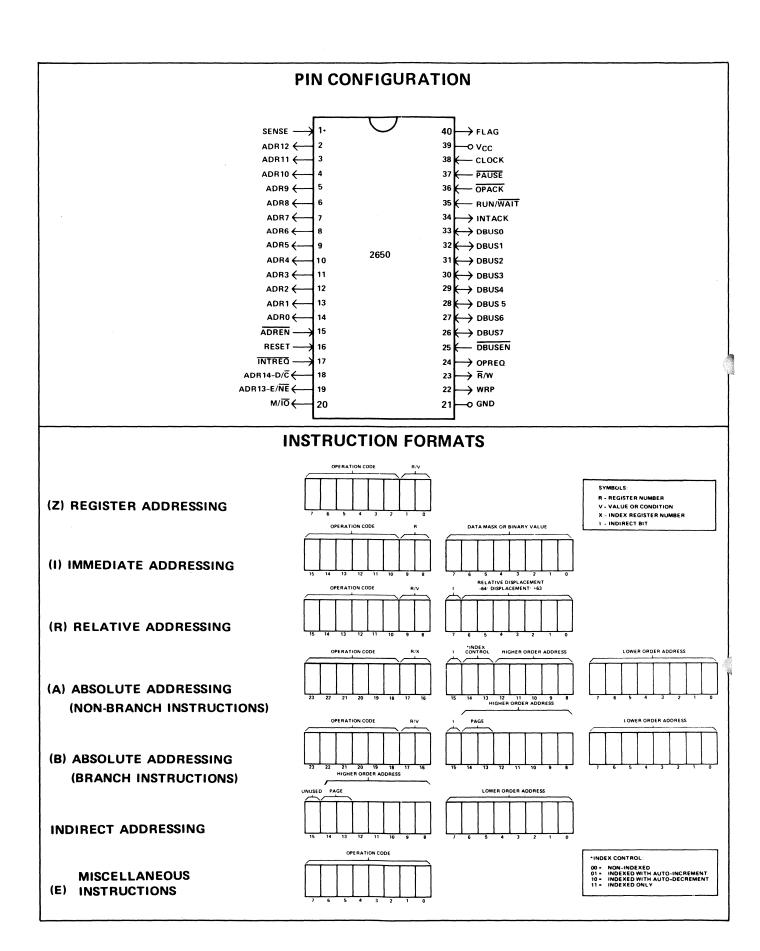

As we know, instructions are made up of one or more 8-bit bytes fed into the instruction register. While a detailed treatment of binary instructions is beyond the scope of this book (the reader is referred to more detailed literature such as the Signetics 2650 MICROPROCESSOR manual), we endeavor in this section to at least give a general flavor of how these instructions are actually structured. (Actual instruction formats are in Appendix A.)

Instructions can be made up of one or more 8-bit bytes which are put (one-at-a-time, of course) into the instruction register. The first byte into the IR basically tells the microcomputer (a) the operation to perform and (b) the number of bytes in the instruction. The second byte in a two byte instruction generally consists of a data value to be operated on.

### Example

The instruction LOAD into register  $R_0$  binary number 10110010 would be written as a two byte binary instruction.

00000100 ← FIRST BYTE: Tells Microcomputer

- a. What to do (LOAD)

- b. Instruction has two bytes (number to be stored is in second byte)

- c. Where to load  $(R_0)$

10110010 ← SECOND BYTE:

Binary Number to be placed in R<sub>0</sub>

There are also single byte instructions:

### Example

We can ROTATE contents of register  $R_0$  one bit to the right with binary instruction:

01010000 ← SINGLE BYTE

- a. Performs ROTATE operation

- b. Indicates single byte instruction

A three byte instruction usually uses the second and third bytes to derive a memory address. Since an address has 15 bits, the third instruction byte can be used for the least significant bits of the address; the remaining bits of the address are taken from 7 least significant bits in the second byte.

### Example

The instruction STORE the contents of  $R_0$  into data memory address 010010101110110 would be written as a three byte binary instruction:

### 11001100 FIRST BYTE:

Instructs store operation and tells computer the following two bytes are a data address.

### 00100101 SECOND BYTE:

Last 7 bits are upper part of address.

### 01110110 THIRD BYTE:

Lower part of address.

Note that the second and third bytes are passed to the operand address register (see Figures 2.6 and 2.8).

MACHINE INSTRUCTIONS

These binary instructions are often called machine instructions.

### Example

Machine instructions for the binary calculator of Figure 2.6 would appear as seen in Table 2.7.

Table 2.7 Example of Instructions

| Machine Instructions             | English Instructions (Figure 2.6) |

|----------------------------------|-----------------------------------|

| 00001100<br>00000000<br>01100101 | ——— LOAD R <sub>0</sub> , 101     |

| 10001100<br>00000000<br>01100110 | ——— ADD R <sub>0</sub> , 102      |

| 01010000 ———                     | - ROTATE RIGHT RO                 |

| 11001100<br>00000000<br>01100111 | STORE R <sub>0</sub> , 103        |

Now the bulk of our design activity with microcomputers is going to be devoted to the writing of instructions. It is rather obvious looking at Table 2.7 that even though the machine instructions are what we finally want in instruction memory, it would be an extremely tedious proposition to write error free instructions.\* It would be certainly easier to somehow write the instructions in English as in the right hand side of the table. We can, in fact, write English-like instructions using the approach discussed in the next section.

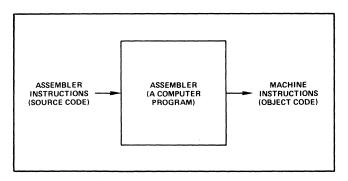

### 2.7 Assembler Instructions

Before discussing how we can write more Englishlike instructions, it is first useful to define a few terms. We have seen that we can write machine instructions.

ASSEMBLER INSTRUCTIONS

We will shortly demonstrate that it is possible to write these in English-like assembler instructions which can then be converted to binary instructions.

In microconverter jargon, we have two "languages" we can use: machine language and assembly language.

**PROGRAM**

The instructions themselves will constitute a program.

ASSEMBLY LANGUAGE

What we will do is the following; we will "write" our program in assembly language

MACHINE LANGUAGE and use another computer (not necessarily the microcomputer) to convert the assembly language to machine language.

ASSEMBLER

The computer that makes this conversion will do so using another program called an assembler.

This conversion process is depicted in Figure 2.10.

SOURCE PROGRAM

Here the assembly language program is often referred to as a source program.

**OBJECT PROGRAM**

The machine instructions (or code) are referred to as the object program.

<sup>\*</sup> The problem can be somewhat alleviated by using an abbreviated notation like hexadecimal. The basic problem of generating error-free code remains.

Figure 2.10 Conversion of Assembler Instructions to Machine Instructions

The assembler converts the source program into binary object program which, in turn, can be placed into the microcomputer instruction memory.

It is beyond the scope of this book to show in detail how to write the basic instructions shown in Table 2.1 in assembly language. (See instead the Signetics 2650 Microprocessor Manual. Also, assembly language instructions are summarized in Appendix A.) We can, however, give the reader insight into the general structure of assembly language by showing the assembly language instructions corresponding to the machine language instructions shown in Table 2.7. We do this in Table 2.8 as follows:

Table 2.8 Assembly Language Instructions for Binary Calculator

| English<br>Instructions    | Assembler<br>Instructions* | Machine<br>Instructions          |

|----------------------------|----------------------------|----------------------------------|

| (Figure 2.6)               | (Source Code)              | (Object Code)                    |

| LOAD R <sub>0</sub> , 101  | LODZ 101                   | 00001100<br>00000000<br>01100101 |

| ADD R <sub>0</sub> , 102   | ADDZ 102                   | 10001100<br>00000000<br>01100110 |

| STORE R <sub>0</sub> , 103 | STRZ 103                   | 11001100<br>00000000<br>01100111 |

The assembler converts these into these.

Note in the table the similarity between the English instructions and the assembler instructions.

To summarize this section, we have demonstrated that the tedium and possibilities for error in writing machine instructions can be eased by writing instructions in assembly language and converting these to binary. Since the bulk of the effort in design with microcomputers comprises programming, the assembler becomes a significant cost/effective design tool.

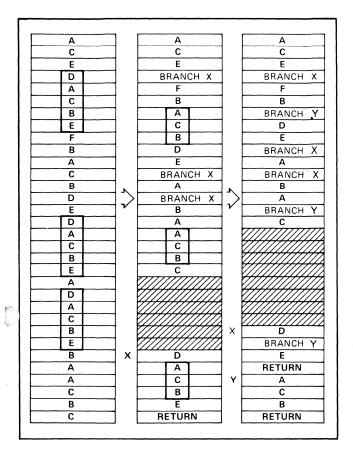

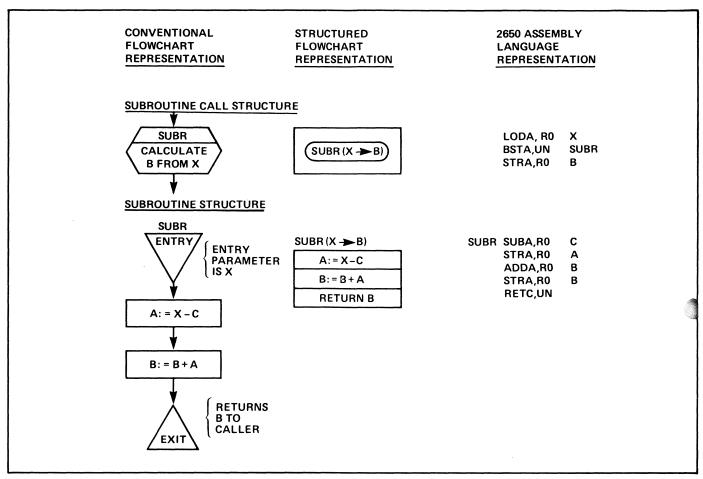

### 2.8 Saving Instruction Memory—The Subroutine

From the previous discussion, we have seen that our microcomputer can address 32,768 bytes. In actual design, however, we will employ only as much memory as is required (i.e., we will attempt to minimize the number of memory chips).

SUBROUTINE

As it turns out, it is almost always possible to reduce the size of instruction memory by employing a programming technique called the subroutine.

This technique can be illustrated by referring to Figure 2.11. Look at the first column in the figure. This column represents a segment of instruction memory with distinct binary instructions which we have labeled A, B, C, D, E. Notice that the boxed instruction sequence D, A, C, B, E appears 3 times, i.e., we are using 15 memory locations to store the same sequence of 5 instructions.

We can reduce the total number of instructions by using a branch command as seen in the second column of the figure. Here, we write the repeated sequence D, A, C, B, E beginning at instruction address X. Each time that the repeated instruction sequence must be executed, we BRANCH to address X and perform the sequence.

RETURN

The instruction following the sequence is a **return** instruction which tells the system to resume executing instructions with the instruction following the last executed BRANCH instruction.

SUBROUTINE

The sequence D, A, C, B, E that starts at location X is called a subroutine.

Compare the first and second columns: we have made the repeated sequence a subroutine and eliminated six instruction memory locations. These

<sup>\*</sup>In the actual application, memory addresses will be written in hexadecimal.

Figure 2.11 Subroutines

saved locations are shaded in the figure. We can make further economies by noting that in the second column, the instruction sequence A, C, B is also repeated. We can further reduce memory by letting A, C, B be a subroutine at location Y as shown in the third column. Note again that the RETURN instruction takes us back to the address immediately following the last BRANCH instruction.

NESTING

Notice in the third column that we have located a subroutine within a subroutine, a process called subroutine nesting.

Observe also that in the third column, we have reduced instruction memory to 75 percent of that used in the first column.

We should point out here that the use of subroutines in this manner is not merely a "frill" but in actuality a technique which can save instruction memory in virtually every microcomputer application.

Let's now turn to an important question: How do

we build this subroutine capability into the hardware we've already developed? The key to this question is the fact that everytime we BRANCH to a subroutine location (X or Y in Figure 2.11) we must somehow save the instruction address that follows the BRANCH instruction (so that we can return to normal operation later).

RETURN ADDRESS STACK We will do this by incorporating a register bank in the system called a return address stack (RAS).

We can conceptualize the return address stack by comparing it to a cafeteria tray holder where clean trays are loaded and extracted from the top of the tray holder. In terms of subroutine operation, we will write the return address on a cafeteria tray and put it on the stack of trays already there. When it is time to RETURN, we will go to the tray holder top and get the return address. If we are nesting subroutines, we will successively place return addresses on trays and push them down on the stack of trays. Each time a RETURN address is executed we will pull the top tray and use its address for the next instruction. It should be clear to the reader that we can nest as many subroutines as we have trays.

The hardware implementation of the return address stack is shown in Figure 2.12. The stack itself consists of a register bank fed by the instruction address register.

STACK POINTER

The specific register employed is governed by a counter called a **stack pointer** which operates (as a rotating counter) to effect the cafeteria tray analogy.

The hardware of Figure 2.12 shows the mechanism by which subroutines are implemented. We can employ this hardware without concern for its operation the instructions noted in the following table.

**Table 2.9 Subroutine Instructions**

| Instruction               | Function                                                                                                                                                     |

|---------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BRANCH to<br>SUBROUTINE X | Causes the program to begin execution of the subroutine beginning at instruction X.                                                                          |

| RETURN                    | Placed at the end of the subroutine Causes return of the program to the instruction address immediately following the last BRANCH to SUBROUTINE instruction. |

Figure 2.12 Implementation of Subroutine Hardware

The use of the subroutine instruction is illustrated in the intelligent typewriter system design discussed in the next chapter.

In the following section, we complete our description of the microcomputer hardware by describing a powerful adjunct to the system, program status.

### 2.9 Program Status Word

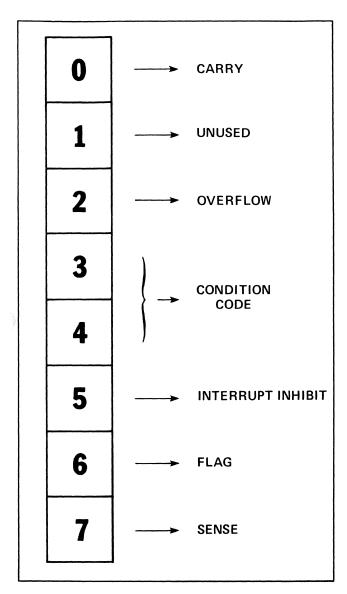

PROGRAM STATUS WORD

As a final element in our microcomputer system, we will add a special purpose reggister which we will call a program status word (PSW).

WORD

(A word is a collection of bits.)

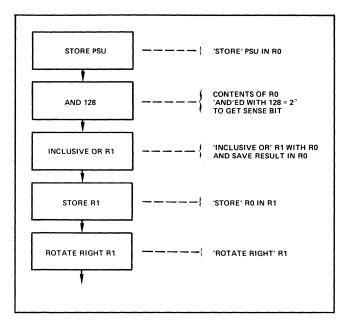

Figure 2.13 Typical Program Status Word

The bits in the PSW can serve a variety of purposes as will be discussed shortly. What is important to first note is that:

- 1. We will be able to put PSW bits into R<sub>0</sub> and vice versa. Hence, computations can be made based on what is in the program status word.

- 2. We will develop instructions that will permit us to test and alter bits in the PSW.

A sample program status word is shown in Figure 2.13 and is 8 bits long (since it will be put in  $R_0$ ). The functions of each, bit are indicated in the figure and described as follows:

| Carry (C)                 | Set by execution of any add<br>or subtract instruction re-<br>sulting in a carry or borrow<br>out of the high order bit<br>of the ALU.                                                                                                   |

|---------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Compare Control<br>(COM)  | Used with COMPARE command: 0 = arithmetic compare; 1 = logical compare.                                                                                                                                                                  |

| Overflow (OVF)            | Employed for signed arithmetic operations; is set when a result exceeds a range of operands.                                                                                                                                             |

| Condition Code<br>(CC)    | Used to interlink COMPARE and BRANCH instructions (See Section 2.4).                                                                                                                                                                     |

| Interrupt Inhibit<br>(II) | As shall be discussed in Chapter III, we can use an external signal to change (i.e., interrupt) the mode of the microcomputer operation. When the interrupt inhibit is set, the system will not respond to an external interrupt signal. |

| Flag                      | The flag bit is a latch driving output to a pin on the micro-processor chip. Use of the flag is illustrated in the next chapter.                                                                                                         |

| Sense                     | This bit is connected directly to a pin on the microprocessor chip.                                                                                                                                                                      |

Note that all bits in the PSW are not used in this microprocessor.

As discussed earlier, we can transfer information between register  $R_0$  and the PSW. This can be done through the following instructions.

**Table 2.10 Program Status Instructions**

| Instruction | Function                                                               |

|-------------|------------------------------------------------------------------------|

| LOAD PS     | Causes current contents of PSW to be replaced with contents of $R_0$ . |

| STORE PS    | Causes contents of PSW to be transferred into $R_{\rm 0}$ .            |

At this point, we have developed a basic microprocessor system. This system is summarized in the next section.

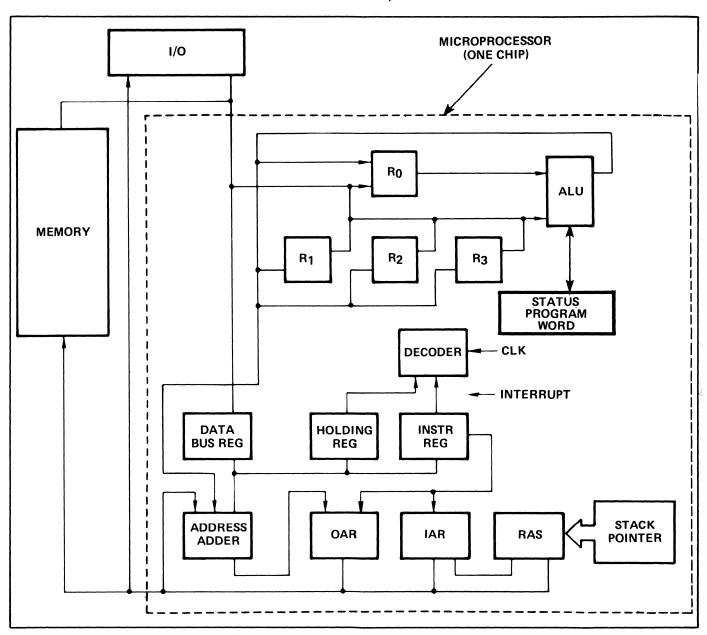

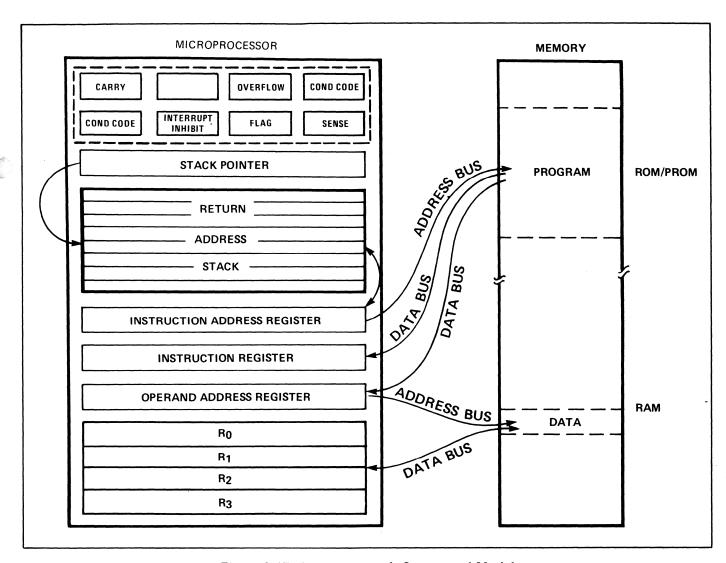

### 2.10 Summary - The Microprocessor

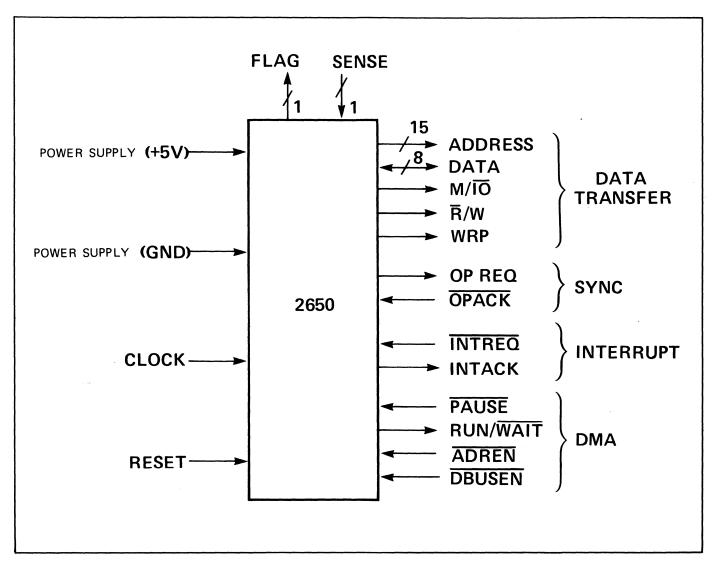

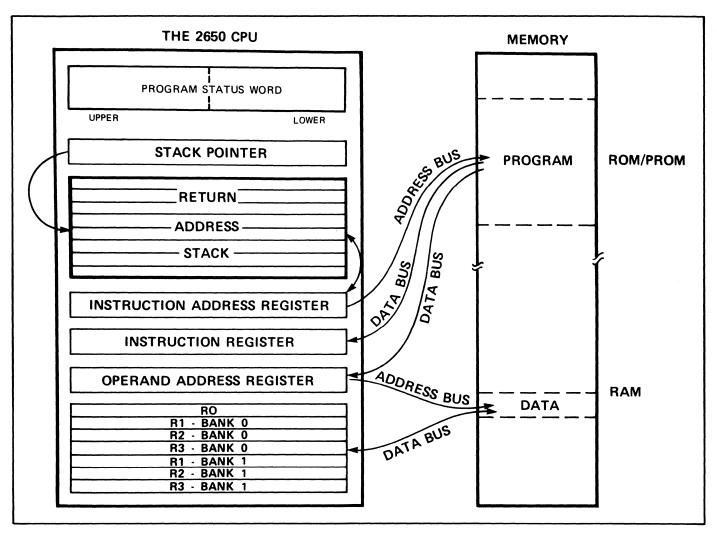

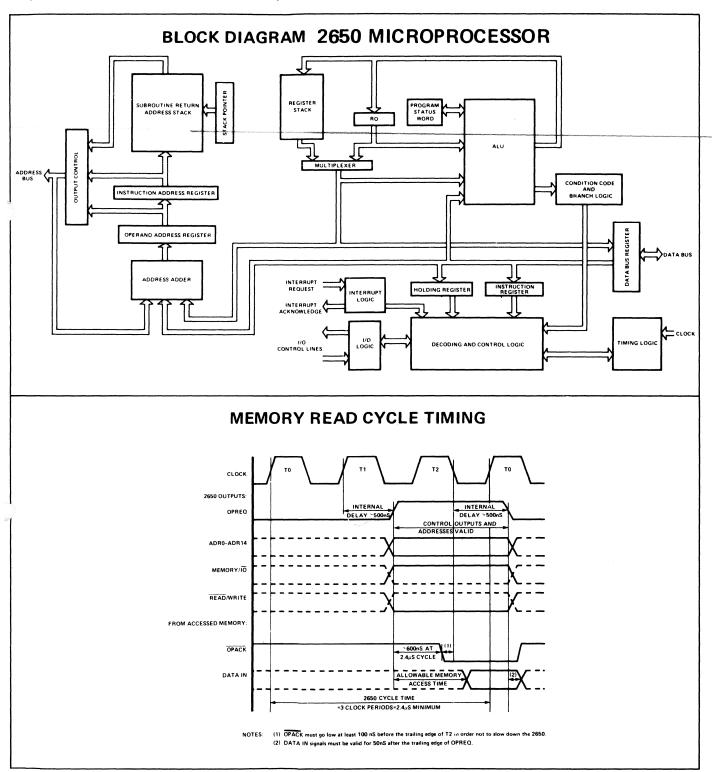

The microprocessor we have developed thus far is shown in Figure 2.14 within the dashed lines. This entire system (i.e., within the dashed lines) is usually made on **one** chip.

The figure includes some additional components not previously discussed. First of these are the holding register and data bus register. These registers are used to hold data and addresses continued

in multi-byte instructions and are a means of transferring data and address from instruction memory onto the data bus and into the OAR, respectively. Second, observe that the figure includes blocks R1, R2, and R3 connected to  $R_0$  and the ALU input. These registers actually comprise two bands of three registers each. They are used as supplements to  $R_0$  (e.g., can be used as source or destination for arithmetic operations, I/O transfer, etc.).

From what has been developed so far, it should be clear that we will design with this microprocessor by:

Figure 2.14 Basic Microprocessor Diagram

- 1. Designing the sequence of instructions, i.e., programming, and

- 2. Designing the electrical interface between the microprocessor and the memory and I/O.

For the first requirement, we really need only the conceptual picture of the unit shown in Figure 2.15 and the instructions. The dashed block in the upper left of the figure contains the program status, discussed earlier. The instructions we have described in the text are summarized in Table 2.11.

The electrical interface design will be made on the basis of the electrical pinouts for the microprocessor chip. This aspect is covered in more detail in the next chapter.

Figure 2.15 A Programmer's Conceptual Model

Table 2.11 Microprocessor Instructions—Summary

| Instruction            | Function                                                                                                                                                     |

|------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LOAD                   | Loads R <sub>0</sub>                                                                                                                                         |

| STORE                  | Places the contents of R <sub>0</sub> into memory                                                                                                            |

| ADD                    | Adds to R <sub>0</sub> what is on data bus and puts result in R <sub>0</sub>                                                                                 |

| SUBTRACT               | Subtracts what is on data bus from R <sub>0</sub> and puts result in R <sub>0</sub>                                                                          |

| AND                    | ''Ands'' what is on data bus with $R_0$ and puts result in $R_0$                                                                                             |

| INCLUSIVE OR           | Performs "Inclusive or" between data bus contents and $R_0$ , putting result in $R_0$                                                                        |

| EXCLUSIVE OR           | Performs "Exclusive or" between data bus contents and $R_0$ , putting result in $R_0$                                                                        |

| COMPARE                | Compares data memory content with R <sub>0</sub> as prerequisite to branch                                                                                   |

| ROTATE RIGHT           | Shifts bits in R <sub>0</sub> one bit to right—least significant bit moves to most significant bit position                                                  |

| ROTATE LEFT            | Shifts bits in R <sub>0</sub> one bit to left—most significant bit moves to least significant bit position                                                   |

| BRANCH                 | Causes instructions to begin execution at another instruction address                                                                                        |

| WRITE                  | Places contents of R <sub>0</sub> onto data bus                                                                                                              |

| READ                   | Places contents of memory (or I/O) into R <sub>0</sub>                                                                                                       |

| BRANCH TO SUBROUTINE X | Causes the program to begin execution of the subroutine beginning at instruction X                                                                           |

| RETURN                 | Placed at the end of the subroutine—causes return of the program to the instruction address immediately following the last BRANCH TO SUB-ROUTINE instruction |

| LOAD PS                | Causes current contents of PSW to be replaced with contents of R <sub>0</sub>                                                                                |

| STORE PS               | Causes contents of PSW to be transferred into R <sub>0</sub>                                                                                                 |

| HALT                   | Stops instruction execution                                                                                                                                  |

### QUIZ FOR CHAPTER II - MICROCOMPUTER BASICS

(Answers on Following Page)

- 1. What is a byte?

- 2. What is an ALU?

- 3. What is a CPU?

- 4. What is I/O?

- 5. What is an instruction?

- 6. What is the function of the LOAD instruction?

- 7. What are MEMORY CONTENTS?

- 8. What is a MEMORY ADDRESS?

- 9. What is AN INSTRUCTION REGISTER?

- 10. What is the distinction between an INSTRUCTION REGISTER (IR) and an INSTRUCTION ADDRESS REGISTER (IAR)?

- 11. What is the function of the OPERAND ADDRESS REGISTER (OAR)?

- 12. What is the difference between a MICROPROCESSOR and a MICROCOMPUTER?

- 13. What is a bus?

- 14. What does a BRANCH XYZ command do?

- 15. What is meant by PROGRAMMING?

- 16. What two basic functions does the ALU perform?

- 17. What are MACHINE INSTRUCTIONS?

- 18. What are ASSEMBLER INSTRUCTIONS?

- 19. What is an ASSEMBLER?

- 20. What is a SUBROUTINE?

- 21. What is the main advantage of the subroutine?

- 22. What is SUBROUTINE NESTING?

- 23. What is a RETURN ADDRESS STACK (RAS)?

- 24. What is the PROGRAM STATUS WORK (PSW)?

- 25. What is DIRECT MEMORY ACCESS (DMA)?

- 26. What is an INTERRUPT?

### ANSWERS TO QUIZ ON CHAPTER II

- 1. A group of binary digits.

- 2. Arithmetic Logic Unit.

- 3. A Central Processing Unit, consisting of an ALU and holding registers.

- 4. Input/Output.

- 5. A group of bits which decoded direct operation of the CPU and other logic.

- 6. Puts data in R<sub>0</sub>.

- 7. The stored bits.

- 8. A group of unique bits that define a specific memory content.

- 9. A register which contains instruction bytes.

- 10. The IR contains an instruction byte; the IAR contains the address of an instruction byte.

- 11. The OAR contains the address of data.

- 12. A MICROPROCESSOR consists of CPU and associated control circuitry; a MICROCOMPUTER consists of a microprocessor, memory, and I/O.

- 13. Parallel lines over which multiple bits can be transmitted (e.g., 8-bit data bus; 15-bit address bus).

- 14. Sets the IAR to XYZ such that the instruction sequence continues beginning with the instruction at address XYZ.

- 15. Designing the sequence of instructions.

- 16. Arithmetic operations and logical operations.

- 17. Binary instructions.

- 18. English-like statements which can be converted to machine instructions.

- 19. A computer program that converts ASSEMBLER INSTRUCTIONS into MACHINE INSTRUCTIONS.

- 20. A subroutine is a subprogram comprising a sequence of instructions that is usually executed more than once during microcomputer operation.

- 21. To save instruction memory.

- 22. The placing of subroutines within subroutines.

- 23. A RAS is a register bank used to store return address during subroutine operation.

- 24. The PSW is a register containing bits corresponding to numerous microprocessor functions.

- 25. DMA is a microcomputer operating mode which permits direct interfacing between memory and I/O.

- 26. A signal to the microprocessor to suspend the current computation and to execute a more urgently needed computation.

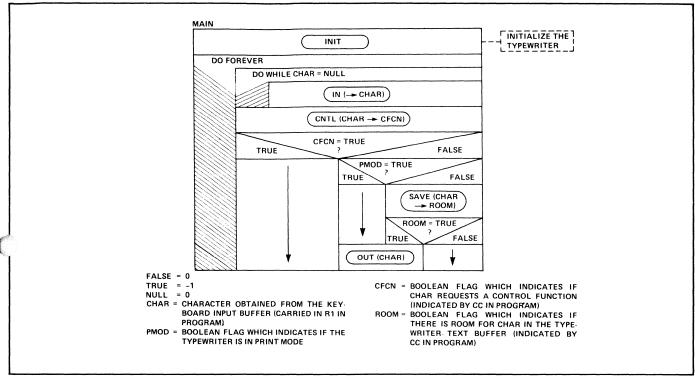

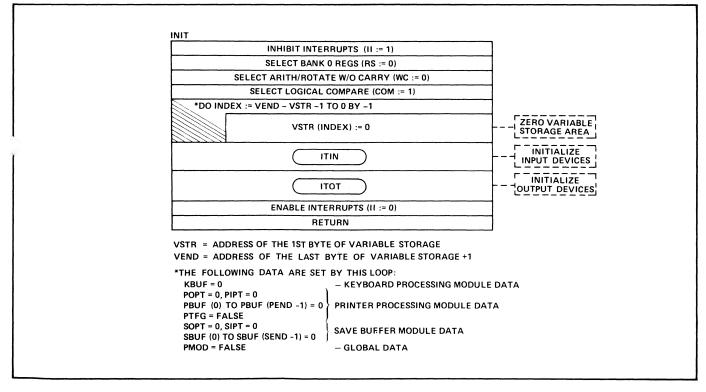

# III. DESIGN AND IMPLEMENTATION OF THE INTELLIGENT TYPEWRITER SYSTEM (ITS)

In the previous chapter, the basic features and capabilities of a typical microprocessor, namely the Signetics 2650, were explained. Now, we can proceed with the design problem posed in Section 1.2 of Chapter I. The relationship between the steps in the microcomputer system development process and the material in this chapter was noted in Figure 1.1. We will begin by considering the interface requirements for the teletype keyboard and typing mechanism; this requirement must be met by both the conventional design using standard circuitry (i.e., LSI, MSI, SSI) as well as that using the microprocessor as a system component. Then, we will consider a system level block diagram of the conventional design and make an estimate of the IC packages required.

At this point, we will begin considering the incorporation of a microcomputer to implement the system specification. The first step will be to select a suitable microprocessor, based on the guidelines that we shall develop. Then, we will describe pertinent features of the selected microprocessor, namely, the Signetics 2650.

Following this, we will consider two possible hardware configurations using this microprocessor. This will be followed by the software program design and implementation details. Finally, we will conclude the chapter by reviewing additional features useful in other classes of applications.

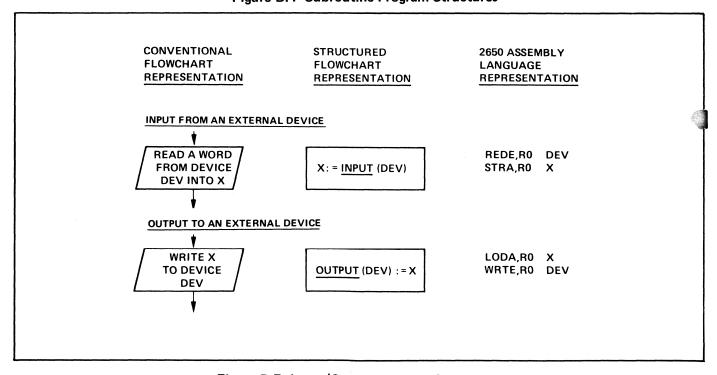

### 3.1 System Overview

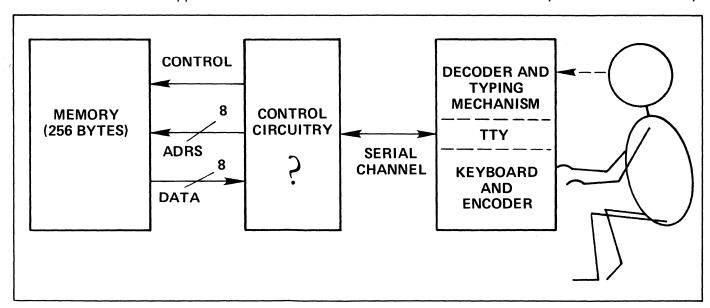

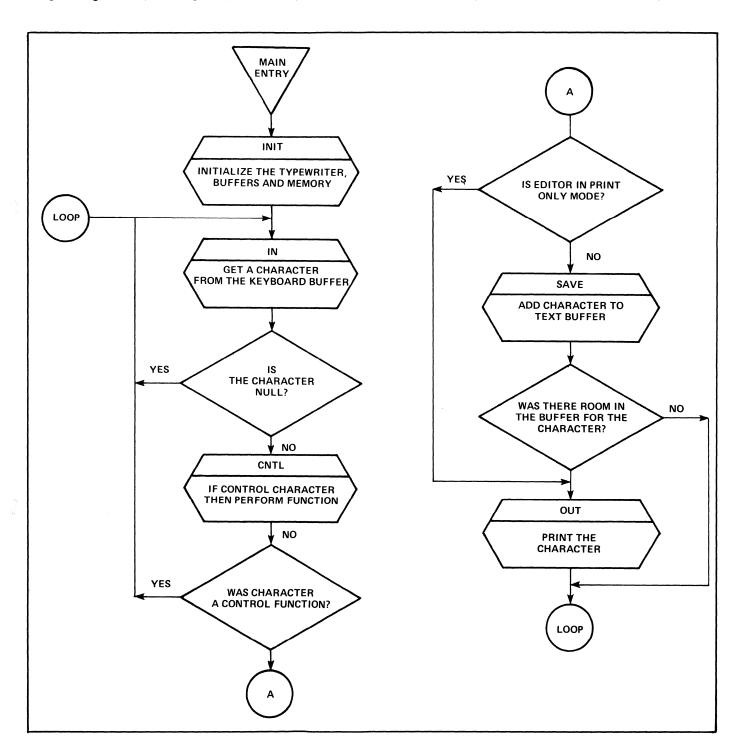

Based on the specification in Chapter II, we can depict the system hardware block diagram, as in Figure 3.1. Essentially, the system consists of a teletype (to enter and type the text), control circuitry (to implement the desired functions) and memory (to store the text).

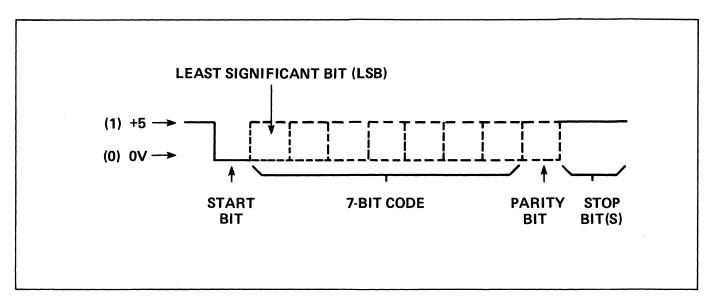

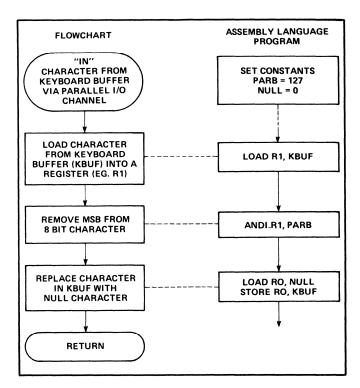

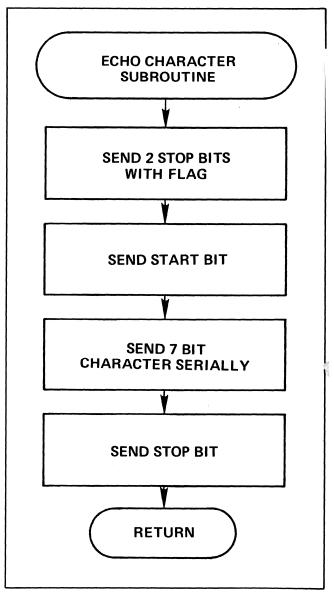

The Teletype (TTY) is a standard device which encodes each of the keyboard character keys into a unique bit pattern which is seven bits long, together with a parity bit (see glossary) for error control. Similarly, when the teletype receives characters encoded in this manner, the typewriter mechanism is activated to print the appropriate symbol.

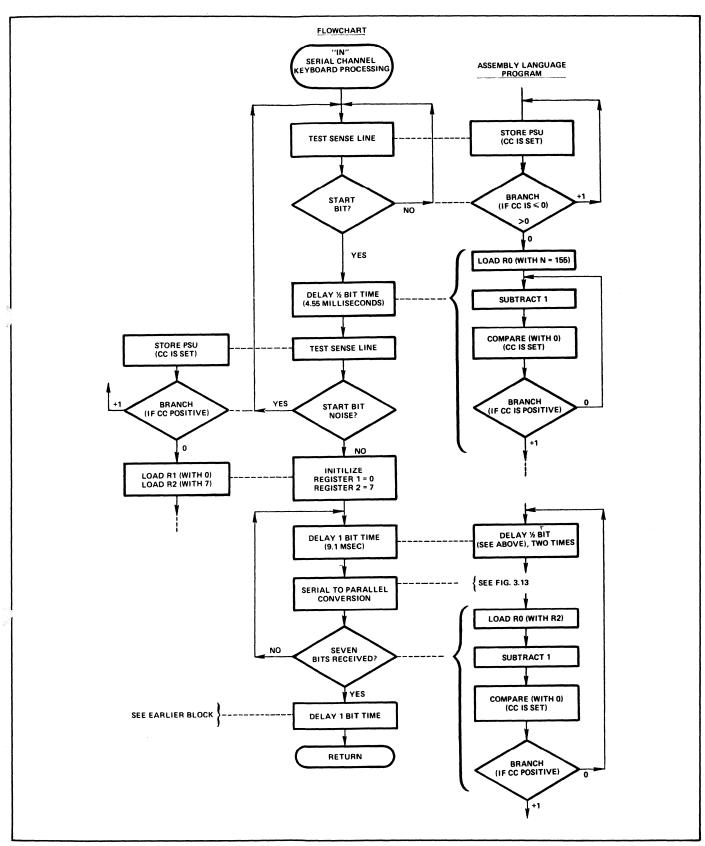

SERIAL I/O

This standardized serial data input/output procedure is graphically depicted in Figure 3.2.

Referring to Figure 3.1, we note that, when the operator pushes a key, a unique serial bit pattern is sent to the control circuitry.

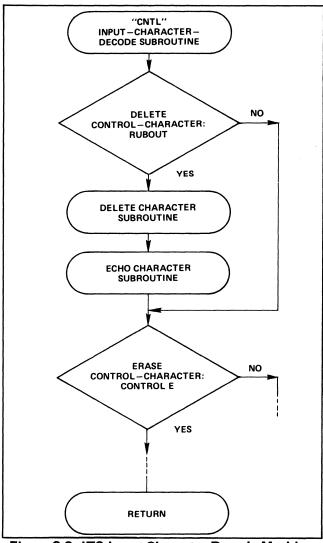

The control circuitry must wait until the entire bit pattern is received and then send it over the same serial channel to the typewriter print mechanism so that the user can visually verify that the correct character was received by the control circuitry.

Figure 3.1 ITS Block Diagram

Figure 3.2 Teletype Serial Data I/O Transfers

**ECHO**

This process of retransmitting the received data is called echoing.

For convenience, a summary of the ITS commands, discussed in Chapter I, is tabulated in Table 3.1. This command specification, together with the teletype serial input/output process described above, gives us adequate information concerning the user and the teletype interface. Referring to Figure 3.1, we note that whatever the hardware implementation of the control circuitry, at least 256 bytes of memory will be required to store the text and the corresponding commands, and then send them back to the teletype print mechanism at the request of the user.

The above description completes the discussion of the common parts of the system implementation. In the following sections, three possible hardware implementations with the associated software details will be considered. The first implementation uses conventional hardware circuitry and, thus, no software is required. Then, after selecting a particular microprocessor, we will describe two microprocessor-based implementations. The first of these implementations, using the Signetics 2650 Microprocessor as a system component, implements a number of functions previously performed by hardware by the microprocessor software program. Then the latter implementation described takes advantage of some of the unique capabilities of the Signetics Microprocessor to significantly reduce the hardware complexity.

**Table 3.1 ITS Command Summary**

| KEY             | FUNCTION                                                                                                                                                                                   |

|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Rubout (delete) | Erase last character in memory and echo the erased character. Additional preceding characters can be erased by continuing to depress the delete key.                                       |

| Control and E   | Erase entire memory.                                                                                                                                                                       |

| Control and B   | Used to indicate beginning of inserted message. Is not printed, but stored in memory. Stops print out when read from memory. Required <b>once</b> for each unique information entry point. |

| Control and C   | Continues print out of memory after entry of unique information.                                                                                                                           |

| Control and P   | Prints out contents of text memory.                                                                                                                                                        |

| Control and R   | Software reset. Clears text buffer and restarts program.                                                                                                                                   |

Note: Bell will ring if any of the following are true.

- 1. Entering more than 250 characters in memory.

- 2. Requesting print out of an empty buffer.

- 3. Attempting to delete more characters than there are in memory.

To keep this text at a reasonable length, we cannot discuss these designs in minute detail; but the material in this chapter, together with that in the appendices, is sufficient to complete the design. Additional material pertinent to this application, including the hardware itself, is available from Signetics Corporation. For the latter microprocessorbased design, we will specifically consider the programming aspects of the serial input/output interface; this will give the reader a flavor for the nature of the software programming task.

### 3.2 ITS Random Logic Implementation

RANDOM LOGIC

Random logic is made up of: (1) SSI circuits such as inverters, gates, and flip-flops,

(2) MSI circuits such as decoders, multiplexers, registers and counters, and

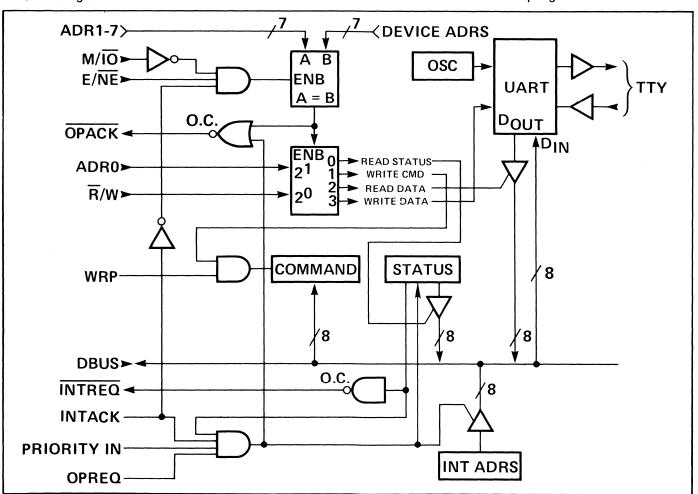

UART

(3) LSI circuits such as memories and universal asynchronous transmitters and receivers (UART).

The random logic implementation of the Intelligent Typewriter System requires, first of all, a serial/parallel converter. This is an LSI integrated circuit which converts from the serial transmission mode (one bit of information at a time) of the teletype to the parallel mode (several bits at a time) of the memory and vice versa.

One possible serial/parallel converter that could be used is the TR1602 asynchronous receiver transmitter. The TR1602 has 40 pins of data lines, control lines, and power supplies. Dual power supplies of +5 and -12 volts are required. Control lines are for receiving and transmitting data, error indications, clock, reset, and data format control.

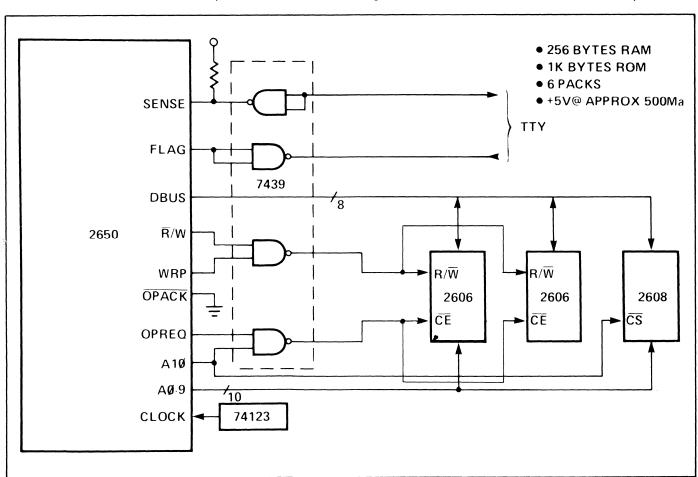

As noted in Section 3.1, for all implementations, each memory word is required to be eight bits wide. A suitable memory component is the Signetics 2606 static RAM. Its organization is 256 words of 4 bits each. So two packages will provide the necessary 256 bytes (8 bits wide) of storage space for the text.

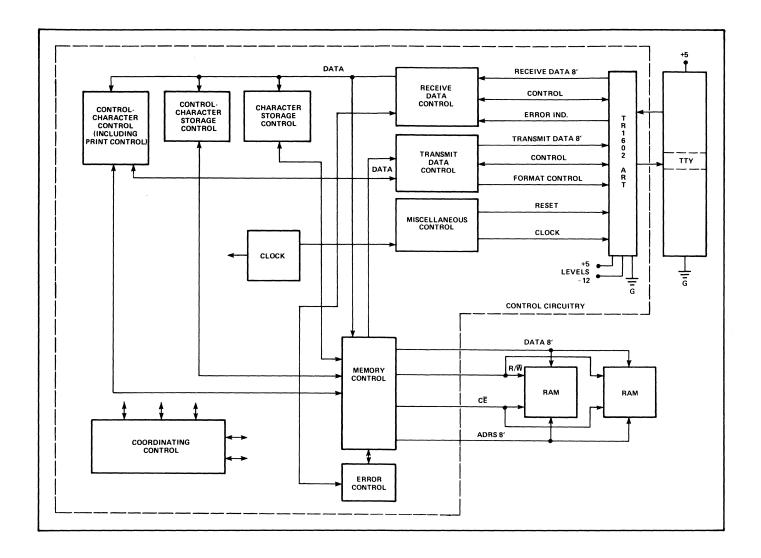

The largest and most complicated portion of the ITS is the control. It can be designed from TTL, SSI, and MSI integrated circuits. Figure 3.3 shows

the hardware block diagram for thie ITS using a conventional logic approach. Remember, each block contains many integrated circuit packages.

First of all, it is necessary to control the TR1602 Asynchronous Receiver Transmitter. The 37 lines of data and control are controlled by three functional blocks: (1) Receive Data Control, (2) Transmit Data Control, and (3) Miscellaneous Control, each controlling its respective function.

A clock is required to drive the TR1602 and possibly the rest of the system. The clock block performs this function.

Memory Control controls the 2606 memory. Addressing the memory, data flow control, read or write operation select, and chip enable are the functions this block provides.

The Character Storage Control block controls storage of characters received from the TTY into memory. These are the characters that will make up the printed page when the print command is issued later.

Control-Character Storage Control controls storage of control-characters received from the TTY into memory. This type of character will not be printed when printout is requested, however. Control characters control page format and provide Stop control (insertion of special user information into the letter after a stop). Control Characters are stored in memory.

The Control-Character Control is a major functional requirement of the ITS. It provides the control functions of character delete, memory erase, continue (after Stop), and printout.

Error control performs the error indication tasks of memory overfill attempt, empty print attempt, and erroneous delete attempt.

The coordinating control block is another major functional block in the ITS. It performs the coordination of all the functional blocks in the system.

In summary, the conventionally designed ITS consists of a TTY, TR1602 serial/parallel interface, a memory, and a large control section. The control section must be large and complex to handle the functions of the ITS. And it must be designed from scratch out of a large array of SSI and MSI circuits such as inverters, gates, flip-flops, multiplexors, decoders, counters, registers, etc. Seventy-five IC

Figure 3.3 Block Diagram—Conventional Implementation for the Intelligent Typewriter System (ITS)

packages are required to implement this random logic version of the ITS.

### 3.3 Selection of a Microprocessor

The process of microprocessor selection involves a rather complex tradeoff between a number of key factors that include (1) the overhead electronics (e.g., input/output interface, clock, power supply), (2) CPU capability (e.g., functional speed, instruction, set, software development tools) and (3) availability (e.g., delivery schedule, second sourcing, cost/volume).